## **EXECUTION SECURITY IN THE SPECTRE ERA**

A dissertation presented in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in the field of

Cybersecurity

by

## Andrea Mambretti

Committee Members Engin Kirda, Northeastern University Guevara Noubir, Northeastern University Aanjhan Ranganathan, Northeastern University Alessandro Sorniotti, IBM Research - Europe Anil Kurmus, IBM Research - Europe Vasileios Kemerlis, Brown University

Northeastern University Khoury College of Computer Sciences Boston, Massachusetts January 2022

#### Northeastern University Khoury College of Computer Sciences

| PhD | Thesis | Approval |

|-----|--------|----------|

|-----|--------|----------|

| Thesis Title:             | Execution Security in         | the Spectre Era                            |

|---------------------------|-------------------------------|--------------------------------------------|

| Author:                   | Andrea Mambre                 | tti                                        |

| PhD Program:              | Computer Science              | _Cybersecurity Personal Health Informatics |

| PhD Thesis App            | proval to complete all degree | requirements for the above PhD program.    |

| Engin Kirda               | Enginderan                    | 01/26/2022                                 |

|                           | Thesis Advisor                | Date                                       |

| <u>Guevara Noubir</u>     | Thesis Reader                 | <u>1/28/2022</u><br>Date                   |

| <u>Aanjhan Ranganatha</u> | n Rhufer<br>Thesis Reader     | 01/28/2022<br>Date                         |

| <u>Alessandro Sorniot</u> |                               | 01/26/2022                                 |

| Anil Kurmus               | Thesis Reader                 | 26 Jan 2022                                |

| Vasileios Kemerlis        | Thesis Reader                 | Date<br>01/26/2022                         |

| Vasteetos Remertes        | Thesis Reader                 | Date                                       |

| KHOURY COLLE              | EGE APPROVAL:                 |                                            |

| A~                        | - Jook                        | 03/31/2022                                 |

| Associate De              | ean for Graduate Programs     | Date                                       |

|                           | D BY GRADUATE STUDENT         | SERVICES:                                  |

|                           | ipient's Signature            | <u>31 March 2022</u><br>Date               |

**Distribution**: Once completed, this form should be scanned and attached to the front of the electronic dissertation document (page 1). An electronic version of the document can then be uploaded to the Northeastern University-UMI Website.

For my parents, Patrizia & Angelo. For my sister Manu, and my brother Marco.

## Abstract

Since early 2018 with the release of new attacks such as Meltdown and Spectre the search for new attack surfaces left the software domain and reached the microarchitectural world. This new type of vulnerabilities exploits bugs, or performance optimizations within the CPU to carry out information disclosure even across privilege domains. This new class of vulnerabilities, referred broadly as *transient execution*, presents a unique challenge because of the lack of details in the microarchitectural realm and tools to study such behaviors. While high level views are available, internal CPU implementations are highly variable from the vendors and the CPU families and often covered by patents.

In this thesis, I provide research into understanding the impact of transient execution attacks in the field of system security. My contributions focus on two specific problems, improving the analysis of transient execution attacks, and understanding their impact on the security of modern systems–i.e., the effects of these attacks on the current existing threat models.

First, I provide a new debug-like technique to study transient execution attacks and reverse engineer the microarchitecture. Leveraging the CPU Performance Monitor Counters (PMCs), I show how it is possible to deterministically observe the side effects of transient execution. I integrate such principle in a new tool, SPECULATOR, that provides the infrastructure to easily build tests to shed light on the microarchitecture internals. Using SPECULATOR, I provide, as results, insights in the microarchitecture internal behaviors, the study of a new Spectre variant called *Split Spectre* and, two new side-channel gadgets–i.e., the Branch Target Buffer (BTB) and the instruction cache (i-cache)– that can be used as alternative to the common data cache.

Second, I provide insights on the effects of transient execution attacks in existing threat models. My effort towards solving this problem is twofold. On the one hand, I study a subset of the Spectre family of attacks, the SPEculative ARchitectural control flow hijacks (SPEAR) and their effect on current memory corruption mitigations–i.e., the Stack Smashing Protection (SSP), the Control Flow Integrity (CFI), and the stack protections in memory safe languages. I show how these mitigations, while mitigating memory corruption vulnerabilities, extend the attack surface in the context of transient execution attacks. My results indicate the need for such mitigations to be re-designed to include transient execution attacks in the threat model.

On the other hand, I present the first study of the transient execution vulnerability checkers. I provide insights in current methodologies–i.e., their strengths and weaknesses–, and show how these tools are not adequate to understand the security stance of a system against transient execution attacks. As a result, I propose a new hybrid tool, called GHOSTBUSTER that overcomes the issues of the state-of-the-art and provides results that are threat model aware.

## Contents

| List of Figures xi<br>List of Tables xiii      |

|------------------------------------------------|

| List of Tables xiii                            |

|                                                |

| Acknowledgements xiv                           |

| 1 Introduction 1                               |

| 2 Background 5                                 |

| 2.1 Microarchitecture                          |

| 2.1.1 Pipeline                                 |

| 2.1.2 Cache                                    |

| 2.1.3 Branch Prediction                        |

| 2.1.4 Out-of-order Execution                   |

| 2.1.5 Speculative Execution                    |

| 2.1.6 Multiprocessing and multithreading       |

| 2.2 Transient execution attacks                |

| 2.2.1 Fault-based attacks                      |

| 2.2.2 Speculation-based attacks                |

| 2.2.3 Speculative Execution Attacks Phases     |

| 2.3 Privilege boundaries and attack impact     |

| 2.4 Defenses                                   |

| 2.4.1 Memory Fencing                           |

| 2.4.2 Branchless masking                       |

| 2.4.3         Retpoline         10             |

| 2.4.4 KPTI                                     |

| 2.4.5 Indirect Branch Restricted Speculation   |

| 2.4.6 Indirect Branch Predictor Barrier        |

| 2.4.7 Single thread indirect Branch Predictors |

| 2.4.8         RSB filling         11           |

| 2.4.9 SSB mitigation                           |

| 2.4.10         PTE inversion         11        |

| 2.4.11 VMC conditional                         |

| 3 | Rela | ated Wo | ork                                                 | 13 |

|---|------|---------|-----------------------------------------------------|----|

|   | 3.1  | Specul  | ative Execution                                     | 13 |

|   | 3.2  | Cache   | Side Channels                                       | 13 |

|   | 3.3  | Specul  | ative Execution Attacks                             | 13 |

|   | 3.4  | Mitiga  | tions                                               | 14 |

|   | 3.5  | Safe Sp | peculation Designs                                  | 15 |

| 4 | Deb  | ugging  | Speculative Execution                               | 17 |

|   | 4.1  | Specui  | LATOR                                               | 18 |

|   |      | 4.1.1   | Performance Monitor Capabilities                    | 18 |

|   |      | 4.1.2   | Objectives                                          | 19 |

|   |      | 4.1.3   | Design and Implementation                           | 19 |

|   |      | 4.1.4   | Triggering Speculative Execution                    | 21 |

|   |      | 4.1.5   | Speculative Execution Markers                       | 21 |

|   | 4.2  | Using   | SPECULATOR: Dissecting the microarchitectural world | 23 |

|   |      | 4.2.1   | Return Stack Buffer Size                            | 23 |

|   |      | 4.2.2   | Nesting Speculative Execution                       | 25 |

|   |      | 4.2.3   | Speculative execution across system calls           | 26 |

|   |      | 4.2.4   | Flushing the Cache                                  | 26 |

|   |      | 4.2.5   | Speculation window size                             | 27 |

|   |      | 4.2.6   | Stopping Speculative Execution                      | 30 |

|   |      | 4.2.7   | Executable Page Permission                          | 30 |

|   |      | 4.2.8   | Memory Protection Extensions                        | 31 |

|   |      | 4.2.9   | Issued vs. Executed $\mu$ ops                       | 31 |

|   | 4.3  | Using   | SPECULATOR: Analyzing Attacks and Mitigations       | 32 |

|   |      | 4.3.1   | SPLITSPECTRE                                        |    |

|   |      | 4.3.2   | BTI                                                 | 33 |

|   |      | 4.3.3   | Mitigations                                         | 33 |

|   |      | 4.3.4   | Out-of-order execution bandwidth                    | 34 |

|   | 4.4  | SplitS  | PECTRE                                              | 35 |

|   |      | 4.4.1   | The SplitSpectre Gadget                             | 36 |

|   |      | 4.4.2   | The Analysis                                        | 38 |

|   | 4.5  | New n   | nicroarchitectural side-channels                    | 41 |

|   |      | 4.5.1   | Icache Attack                                       | 42 |

|   |      | 4.5.2   | Icache Discussion                                   | 42 |

|   |      | 4.5.3   | Double BTI Attack                                   | 44 |

|   |      | 4.5.4   | Practical considerations                            | 47 |

|   | 4.6  | Gadge   | ts analysis                                         | 48 |

|   |      | 4.6.1   | Icache Attack                                       | 48 |

|   |      | 4.6.2   | Double BTI Attack                                   | 49 |

|   | 4.7  | Mitiga  | tions                                               | 51 |

| 5 | Imp  | bact of Spectre 53                                                                                                                                                                    |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.1  | Speculative execution attacks on memory safety mechanisms                                                                                                                             |

|   |      | 5.1.1 SPEAR attacks                                                                                                                                                                   |

|   |      | 5.1.2 Speculation window and eviction                                                                                                                                                 |

|   |      | 5.1.3 Speculative ROP                                                                                                                                                                 |

|   | 5.2  | Case studies                                                                                                                                                                          |

|   |      | 5.2.1 Attacking stack canaries                                                                                                                                                        |

|   |      | 5.2.2 Attacking CFI                                                                                                                                                                   |

|   |      | 5.2.3 Attacking memory safe languages                                                                                                                                                 |

|   |      | 5.2.4 SPEAR attack against Rust bounds checking                                                                                                                                       |

|   | 5.3  | Mitigations against SPEAR                                                                                                                                                             |

|   |      | 5.3.1 Mitigations for SSP                                                                                                                                                             |

|   |      | 5.3.2 Mitigations for the Go compiler                                                                                                                                                 |

|   |      | 5.3.3 Mitigations for GCC VTV                                                                                                                                                         |

|   | 5.4  | Discussion on SPEAR                                                                                                                                                                   |

|   | 5.5  | Testing Tools    82                                                                                                                                                                   |

|   |      | 5.5.1 Information gathering tools                                                                                                                                                     |

|   |      | 5.5.2 Empirical tools                                                                                                                                                                 |

|   | 5.6  | Methodology                                                                                                                                                                           |

|   |      | 5.6.1 Use Cases                                                                                                                                                                       |

|   |      | 5.6.2 Systems and Platforms                                                                                                                                                           |

|   | 5.7  | Testing Tools Analysis    84                                                                                                                                                          |

|   |      | 5.7.1 Tools comparison                                                                                                                                                                |

|   |      | 5.7.2 Analysis                                                                                                                                                                        |

|   | 5.8  | Recommendations                                                                                                                                                                       |

|   |      | 5.8.1 Limit cache noise                                                                                                                                                               |

|   |      | 5.8.2 Define the right use case and understand your threat model 92                                                                                                                   |

|   |      | 5.8.3 Understanding information gathering tools results                                                                                                                               |

|   |      | 5.8.4 Use a mixed approach                                                                                                                                                            |

|   |      | 5.8.5 Static analysis                                                                                                                                                                 |

|   | 5.9  | GhostBuster                                                                                                                                                                           |

| 6 | Futu | are Work 97                                                                                                                                                                           |

| 7 | Pape | ers 99                                                                                                                                                                                |

| / | 7.1  | Related Publications   99                                                                                                                                                             |

|   | 7.2  | Other work         99                                                                                                                                                                 |

|   | 1.4  | 7.2.1 Lava: Large-scale automated vulnerability addition [1] 100                                                                                                                      |

|   |      | <ul> <li>7.2.1 Lava: Large-scale automated vulnerability automity automition [1]</li> <li>7.2.2 HotFuzz: Discovering Algorithmic Denial-of-Service Vulnerabilities Through</li> </ul> |

|   |      | Guided Micro-Fuzzing [2]                                                                                                                                                              |

|   |      | 7.2.3 Trellis: Privilege separation for multi-user applications made easy [3] 100                                                                                                     |

|   |      | 7.2.4 HONEYBUG: hypervisor-based approach for gathering attacker insights . 102                                                                                                       |

|   |      |                                                                                                                                                                                       |

#### 8 Conclusions

## Bibliography

# List of Figures

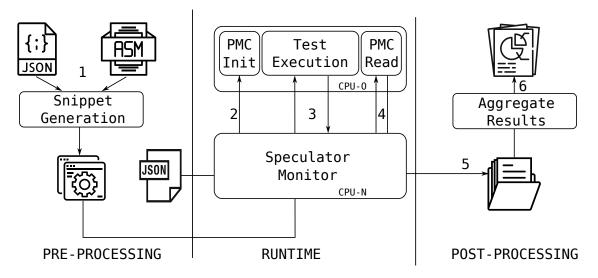

| 4.1  | The architecture of SPECULATOR. A template with the speculative execution trigger and a list of instructions to be speculatively executed are the input to the code generation. The code snippets are run repeatedly under supervision of the speculator monitor, which captures the event specified in the configuration file. Finally, the measurements are post-processed to present a final report on speculative execution behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

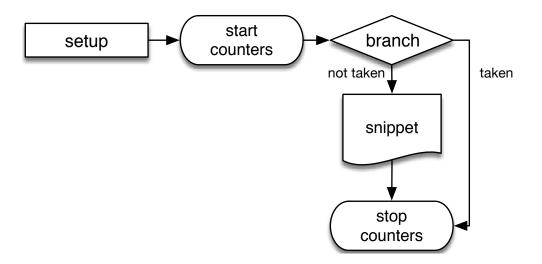

| 4.2  | Flow chart of one of the experiment template used in SPECULATOR. The setup code brings the branch predictor in a specific state that will cause the later branch to mispredict and speculatively execute the code snippet consisting of the instructions. The speculative execution of the instructions is measured by the PMC infrastructure, which is triggered by the corresponding start/stop instructions indicated in the flow chart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22       |

| 4.3  | Return Stack Buffer test on Kabylake.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25       |

| 4.4  | Return Stack Buffer test on AMD Ryzen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25       |

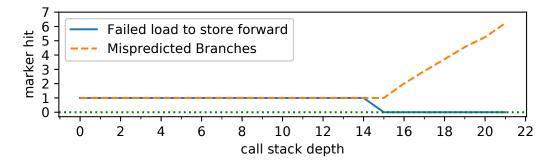

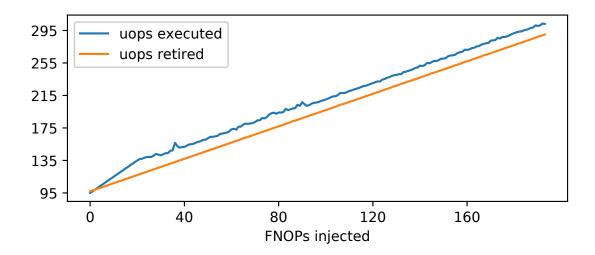

| 4.5  | Speculation window of a store-to-load forward failure, measured in executed <i>FNOPs</i> on Broadwell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30       |

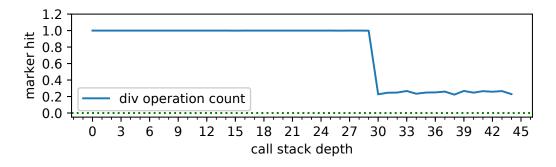

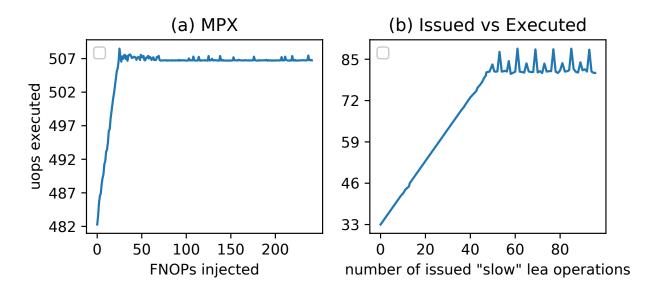

| 4.6  | a) Speculative execution after an MPX bounds violation. b) Performance counter<br>numbers for an increasing number of speculatively executed relative load instruc-<br>tions. The graph shows that the number of issued instructions corresponds to the<br>number of executed instructions, justifying the use of such instructions as markers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32       |

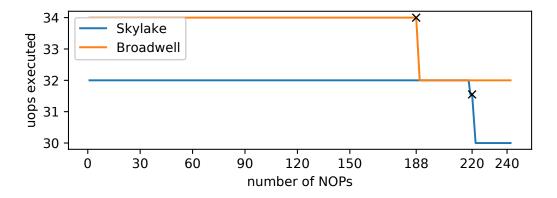

| 4.7  | Reorder buffer size test results on Broadwell and Skylake. Since the marker instruction is no longer executed for a sufficiently large number of <i>NOPs</i> , the number of executed $\mu$ ops drops at the size of the reorder buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35       |

| 4.8  | RSB test on Broadwell. As in the AMD case, Broadwell is able to predict the location of my target even if the RSB is empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36       |

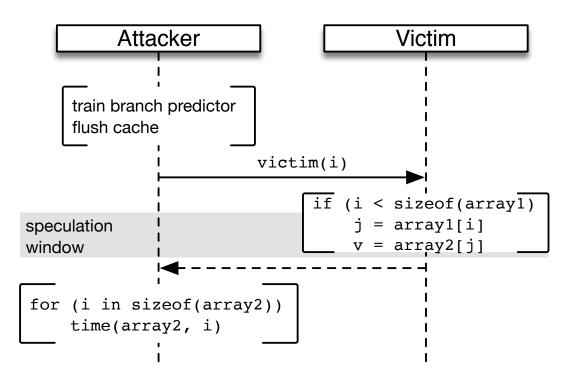

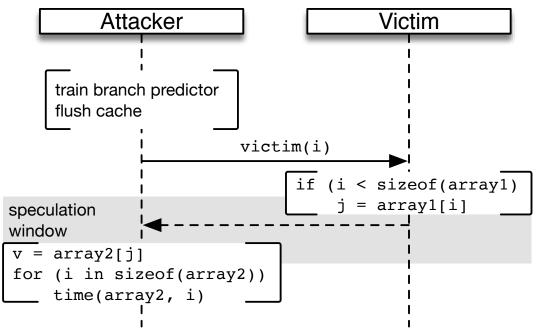

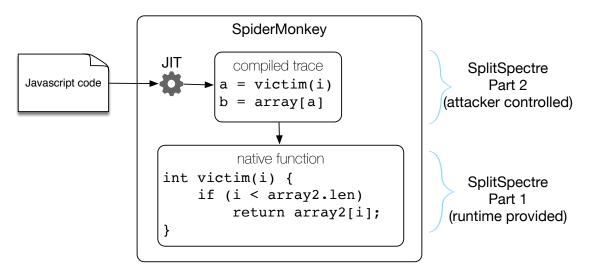

| 4.9  | A comparison of regular Spectre v1 and SPLITSPECTRE. While SPLITSPECTRE only requires a simple array access, the speculation window needs to be sufficiently large to contain both the gadget and the second array access exercised by the attacker.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37       |

| 4 10 | attacker.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 37<br>38 |

| 1.10 | reconceptual view of a orbitor berne attack instance with Javasenpt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50       |

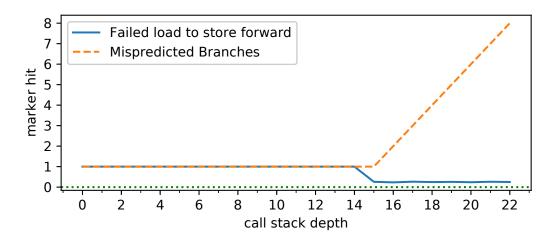

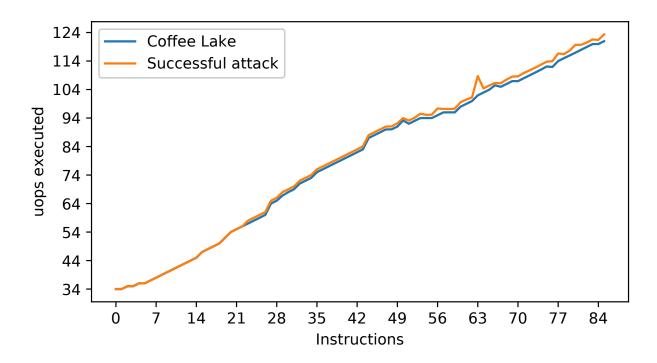

| 4.11                                | An examination of the SPLITSPECTRE execution trace between the length check of <i>string.charCodeAt_impl()</i> and the second array access using SPECULATOR. The graph shows my results of the test on a Coffee Lake machine. It shows that, on average, I are not reaching the second array access in speculative execution. The small spikes in the graph are caused by mispredicted branches in the trace itself, which lead to nested speculative execution of fast-executing code paths. | 39             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.12                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41             |

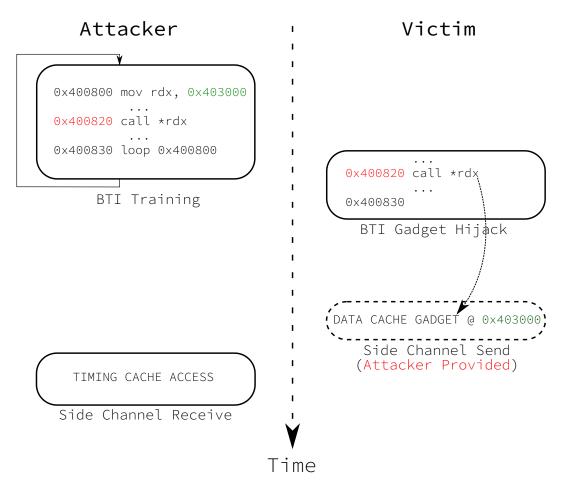

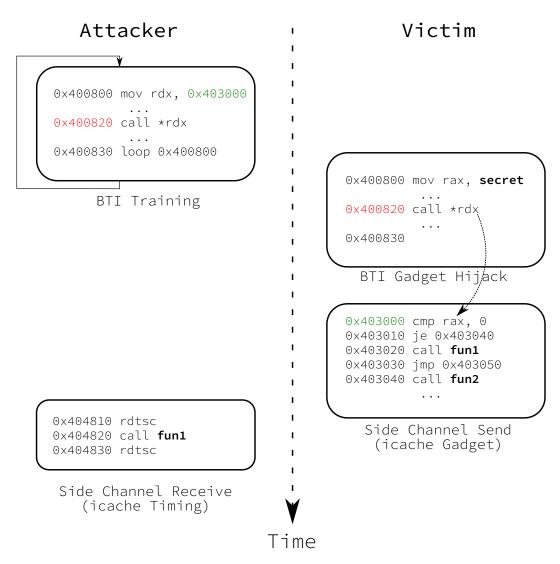

| 4.13                                | Description of the icache attack: the attacker performs BTI at first; the victim speculatively executes one of two functions depending on the content of a register; the attacker later times the execution of either function to learn one bit of the                                                                                                                                                                                                                                        |                |

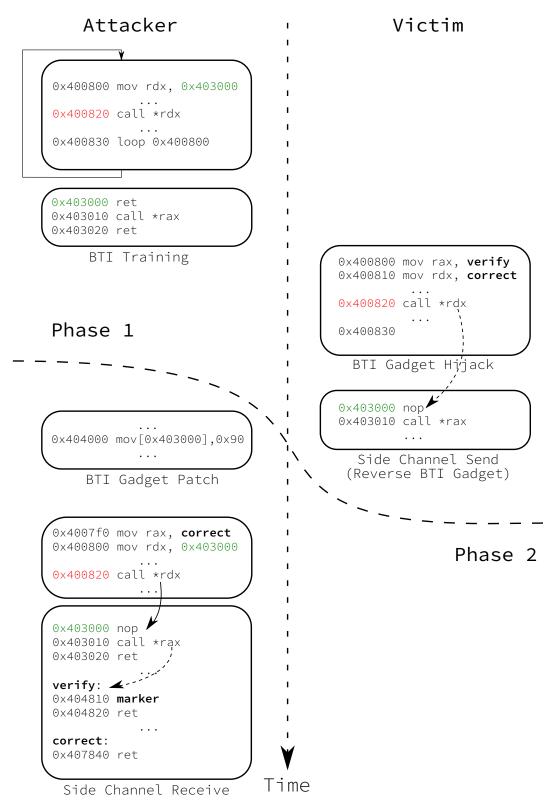

| <ul><li>4.14</li><li>4.15</li></ul> | condition register                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43<br>45<br>47 |

| 4.16                                | Double BTI attack success rate on leaking a one byte of secret                                                                                                                                                                                                                                                                                                                                                                                                                                | 50             |

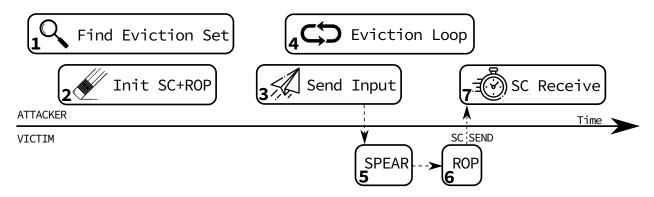

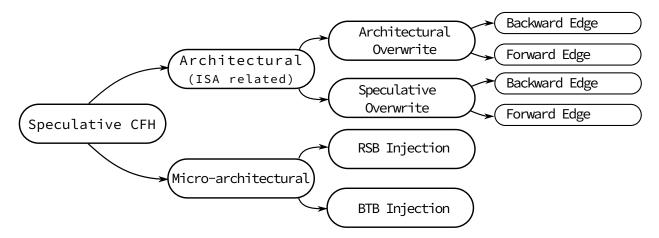

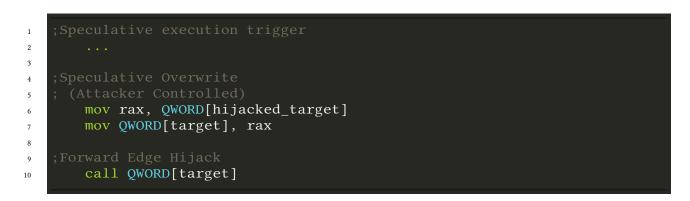

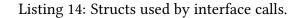

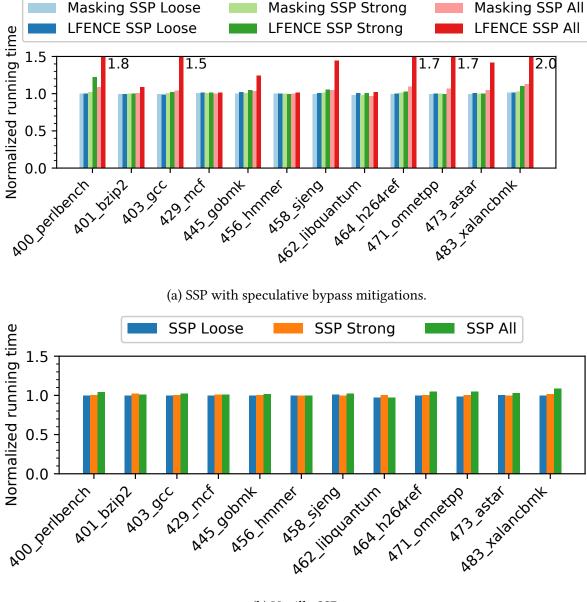

| 5.1<br>5.2<br>5.3<br>5.4            | Overview of speculative attack against memory safety mechanisms Overview of various Speculative control flow hijacking attacks Overhead computed as normalized runtime over SSP Disabled baseline Empirical CDF of the logarithm of the overhead percentage for the considered                                                                                                                                                                                                                | 55<br>56<br>77 |

| 5.5                                 | mitigations. Overhead data is gathered by running the full set of benchmarks of<br>the Go runtime version 1.12.0                                                                                                                                                                                                                                                                                                                                                                              | 79             |

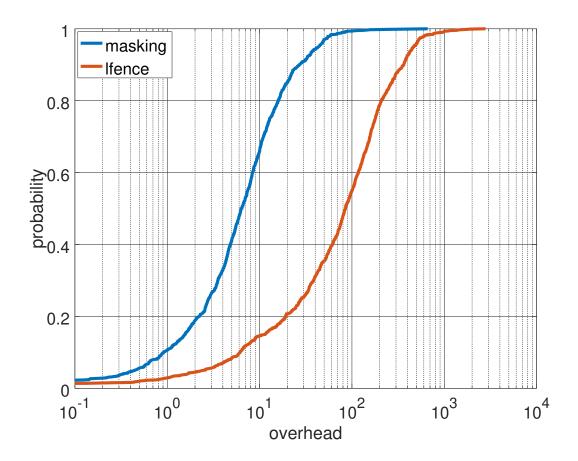

|                                     | GHOSTBUSTER while with dotted circles I highlight operations performed.                                                                                                                                                                                                                                                                                                                                                                                                                       | 91             |

# List of Tables

| 4.1 | The CPUs per architecture I use Speculator on. While Haswell and Skylake are<br>new designs – "tocks" in Intel nomenclature – Broadwell is a "tick", a die-shrink of<br>Haswell. Kaby and Coffee Lake are instead optimized versions of Skylake design<br>within the same die size                                                                                                                                 | 24 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Speculation window of a conditional branch depending on the type of instructions needed to resolve the branch as well as the placement of the value involved in the condition, measured in cycles.                                                                                                                                                                                                                 | 29 |

| 4.3 | Speculation window of an indirect control flow transfer, measured in cycles. The speculation window size depends on where the target of the indirect control flow transfer is stored.                                                                                                                                                                                                                              | 29 |

| 4.4 | Success rates for the SplitSpectre attack on JavaScript. I perform 100 runs, each run trying to leak a string of 10 consecutive characters. I provide numbers on both the highest and the second highest scoring characters.                                                                                                                                                                                       | 40 |

| 4.5 | icache attack experiment with a gadget from <i>libhttp-parser.so</i> : each row displays the success rate in guessing the value of the victim's secret. The success rate is computed as the rate between samples displaying an icache hit (resp. miss) when the value of the victim's secret is 0 (resp. 1). An icache hit is defined as an execution of the icache gadget timed below a pre-determined threshold. | 49 |

| 4.6 | Default STIBP settings in the kernel used by the distributions tested in my evaluation                                                                                                                                                                                                                                                                                                                             | 51 |

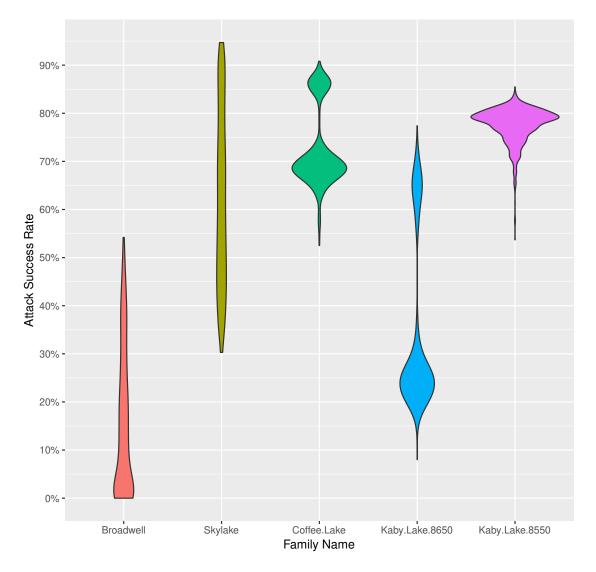

| 5.1 | Success rate (in percentage) computed over 1000 iterations for architectural or speculative overwrites of backward and forward edges performed on various architectures families.                                                                                                                                                                                                                                  | 59 |

| 5.2 | ROP gadgets used for building Spectre v1 chain with their corresponding occur-<br>rences. The search space is a subset of <i>libc</i> , <i>libpng</i> , <i>libz</i> and <i>ld</i> executable pages,<br>obtained by filtering out pages unmapped in the victim's address space and pages<br>without a valid TLB mapping.                                                                                            | 65 |

| 5.3 | CPU families the tools have been tested with the corresponding kernel version                                                                                                                                                                                                                                                                                                                                      | 83 |

| 5.4 | Major pitfalls and limitations observed for each tool. I indicate with $\checkmark$ that the pitfall is present, whereas I leave blank otherwise.                                                                                                                                                                                                                                                                  | 85 |

| es               |                                          |

|------------------|------------------------------------------|

| g                |                                          |

| n                |                                          |

| n                |                                          |

| e                |                                          |

| e                |                                          |

|                  | 86                                       |

|                  | 88                                       |

|                  | 89                                       |

| ו<br>1<br>1<br>2 | es<br>ng<br>on<br>an<br>oe<br>oe<br><br> |

## Acknowledgments

Some people might think that a PhD dissertation like this one is simply the result of the author's hard work throughout several years of research. While this is partially true, there is always way more behind the scene. I strongly believe that my work is also the outcome of the environment I had the luck to live in. The environment mostly being all the great people I had the pleasure to meet and learn from in my life. Here, I would like to try to acknowledge each and everyone of these people.

First and foremost, I would like to thank my parents, my mom Patrizia and my dad Angelo that through their hard work and amazing guidance allowed me to pursue my dreams and achieve all the things I had without any pressure or any constraint. I would like also to thank my sister Emanuela, my brother Marco, my brother-in-law Dario, all my cousins, and all my grandparents Caterina, and the late Alice, Giovanni and Federico for always being there supporting me. A special thanks also goes to Anna, Carolina, Danilo, and Vittorio for being my second family since many years and that, despite everything, never really left my side.

Beyond my family, I had the extreme luck to find on my path great advisors that directed me all the way here. Above all, I would like to thank my PhD advisor Engin Kirda which accepted me in his group and since 2014 has been advising and supporting me, and showed me the ropes of how to be a good researcher. Also, thanks for the great Netflix suggestions!!! ;-).

During my years of studies in Milano, I had the pleasure to encounter on my path Federico Maggi, Stefano Zanero, Marco Domenico Santambrogio, Davide Basilio Bartolini, Filippo Sironi, Francesco Trovò and Alessandro Barenghi that put me in contact with the security and the research worlds, and pushed me to pursuit a PhD.

From my time in Boston, I would like to thank Michael Weissbacher, Patrick Carter, Collin Mulliner, Tobias Lauinger, Amin Kharraz, Abdelberi Chaabane, Kaan Onarlioglu, Walter Rweyemamu, Andrew Fasano, Arash Molavi, Konstantinos Athanasiou, Christina Dimovasili, Andreas ten Pas, Sammie Katt, Molly Ohman, Yorgos Zirdelis, Yorgos Efthymiadis, William Lee, Domien Schepers, Andrea Baisero, Ahmad Bashir, William Blair, Manuel Egele, Wil Robertson, Joshua Bundt, Tim Leek, Erik-Oliver Blass, Guevara Noubir, Piotr Sapieżyński, Luciana Kiffer, Dimitris Tsipras, Raul Quadra, Daianne Maia, Claudia Marino, and Claudia Tomsa. Everyone of you made me feel at home and enjoy each and everyone of the days I spent in the US.

This dissertation would not have been possible without my amazing friends, colleagues, and mentors from IBM Research Anil Kurmus, Alessandro Sorniotti, Matthias Neugschwandtner, and Alexandra Sandulescu. To many more papers together! Also, from the big IBM Research family I would like to thank Chrysa Stathakopoulou, Kaoutar Elkhiyaoui, Angelo De Caro, Marcus Brandenburger, Marc Stoecklin, and Ellie Androulaki for making IBM Research such a special place.

From my time in Zürich, I would like to thank Teri Andos, Christina Haupt, Valentina Marchionni, Davide Basilio Bartolini (again), Carlo Ciaccia, Kostantinos Tsoukalas, Yashashwa Pandey. If there was someone that could have made my decision to move back to Europe easier, it was you.

My passion for computers goes back all the way to my first Commodore64 we first got in '92/93. During those very early years of my life, through my father's passion for technology and electronics, I had the pleasure to come in contact with two very special people, the late Daniele Rizzo and Davide Butti. The first two hackers I met in my life. From them I learned, directly and indirectly, more than they can ever imagine.

This dissertation and the rest of the work I generally do is filled with C code or assembly language. Most people try to avoid such languages because tedious and painful to use. At the contrary, I fell in love with them during my early programming experience in High School, and never wanted to leave them ever since. A big part of my love for low level languages and therefore low level system security comes from my excellent High School teacher Virginia Bacchini which with extreme clarity and passion start me with programming and her lessons stayed with me all the way until now.

## Chapter 1

## Introduction

In early 2018, the release of the Spectre [4, 5] and Meltdown [6] vulnerabilities deeply shook the system security world. These new transient execution vulnerabilities are differently rooted than the very well studied and understood memory corruption vulnerabilities. They exploit side effects caused by modern CPU performance optimizations (e.g., *out-of-order* and *speculative* execution) and not bugs within a code base. Transient execution vulnerabilities concern the confidentiality of a program and not its integrity. Generally, whenever the CPU guesses incorrectly during the application of one of these performance optimizations, it needs to roll-back the micro-architecture status and squash the transient instructions involved. The problem that transient execution attacks leverage is that the status of the micro-architecture is never fully restored to the point before the guess has taken place. This incomplete operation leaves some visible side effects that are function of the accessed data and the code that was mistakenly executed. An attacker using one of the many side/cover channels available can reconstruct possible secrets from those side-effects.

One of the most prominent transient execution attacks is Meltdown. It rely on the fact that due to *out-of-order* execution the CPU does not stop executing in case of a fault until the faulty instruction retires. This has been shown to allow information leakage between different privilege levels (e.g., user and kernel space) that the fault should have prevented. Meltdown and its variants are powerful and relatively easy to carry out. However, they are also easy to mitigate in software [7] (arguably with high overhead), or to fix in hardware in future CPUs by verifying the fault during speculation and not at instruction retirement. Intel has released fixes in its 9 series of CPUs while AMD was never vulnerable to this type of attack.

Another notorius transient execution attack is Spectre. Spectre and its variants do not target a bug within the CPU as Meltdown but code patterns that can cause speculative execution to mi-speculate towards sensitive code that can leak information through covert channels. Given the nature of Spectre-like attacks, they are hard to efficiently mitigate and therefore, as it has been for the buffer overflow, they will not go away anytime soon. Spectre attacks affect any CPU that supports speculative execution. Mitigations against Spectre attacks are available but due to their high overhead are generally not applied, or left disabled by default.

In general, studying such new vulnerabilities present several challenges. The lack of details of the CPU micro-architecture requires extensive and tedious reverse engineering of all the internal components and their behavior in the context of out-of-order and speculative execution. This process is made even more challenging due to the lack of tooling to directly control the microarchitecture internal components leaving the researchers with just the noisy covert channel option to verify their findings. Finally, even within the same hardware manufacturer the behavior of each CPU changes across families due to internal design changes. This forces the reverse engineering effort to be repeated across several CPU models.

Transient execution attacks are able to break the process to process isolation that is part of the security guarantees the CPU provides at the operating system. Process to process isolation is one of the building blocks for modern defense mechanisms and its breach is not accounted in many existing threat models. The ability of Spectre and Meltdown to bypass the isolation has forced the security community to revise their security threat models to verify they still hold in the new Spectre era. However, even simply understanding if a system is actually protected against Spectre and Meltdown is rather complicated. Few tools are available but correctly understanding their results can be confusing and misleading for system operators. An interpretation mistake can cause either a false sense of security or, huge performance penalties even when there is no actual threat. Improvements are necessary in this area to enable system administrators and security researchers to obtain a better picture of the system status.

**Thesis Statement.** It is fundamental to have a deterministic view on transient execution to achieve fast and precise micro-architecture reverse engineering that is the basis for exploring new attack techniques, and analyze and improve defense mechanisms.

For the purpose of my thesis, I propose to enhance the state of the art in the following areas:

- **Speculative execution analysis:** The first step towards understanding the extent of these attacks requires the ability to reliably observe the speculative execution side-effects within the micro-architecture. While for memory corruption vulnerabilities there are several tools like *gdb* that allow to investigate program crashes, nothing is currently available to analyze speculative execution and inside the micro-architecture. Related work rely on the very noisy covert channels to study these attacks and do not decouple any of the phases the attack is composed making the attacks hard to analyze in details. In essence, using covert channels adds another source of non-determinism besides the never fully controllable predictors the attack is leveraging. Attributing the cause of a failed attack observation to either problems in training the predictor, or in using covert channel is often impossible. Having a deterministic way of observing the side-effects of mispeculation greately reduces the complexity on analyzing attacks by limiting the possible root causes of failure. In this area, I provide the first methodology that allows to observe the speculative execution side-effects and to dissect each phase of the attack independently. This enables a debug-like approach and helps to clarify the role of each of the phases of the attack in the overall success and feasibility. I integrate this technique in a novel tool that I then use to investigate several micro-architectural behavior as well as a new Spectre variant called Split Spectre and two new side channels gadgets to build the covert channel.

- **Understanding Spectre's impact:** In this dissertation, I investigate in which way the security threat models are impacted by the discovery of transient execution vulnerabilities. First, I analyze common defenses against memory corruption vulnerabilities (e.g., CFI or SSP) and show how, while defending from memory corruption vulnerabilities, they extend the attack surface in the transient execution context. I show how these defenses require a re-design

in the Spectre era. Furthermore, I provide the first comparison of the available transient execution vulnerability checkers and their underlining methodologies. I describe the pitfalls all the available tools have and I propose a new guideline for building checkers to prevent common mistakes. Finally, I introduce a new tool that builds upon related work to overcome the individually identified pitfalls.

## **Chapter 2**

## Background

## 2.1 Microarchitecture

The microarchitecture can be generally refer to as a specific implementation of an Instruction Set Architecture (ISA). The ISA can be viewed as an high level description of a computer architecture. For instance, *x86-64* is one of the most popular ISA used today and can be found under two different microarchitectural implementations, one provided by Intel and the other provided by AMD. Based on the ISA that is aiming to implement, a modern microarchitecture contains a certain number of registers, a caching hierarchy, one or several communication busses, a set of decoding and executions units related to the instructions that are expected to be executed, and a series of components and optimization designs that aim to boost its performance. Instances of such performance enhancer optimizations can be branch predictor units, out-of-order execution, or speculative execution.

Today's microarchitectures try to optimize every clock cycles by applying extensively optimizations. Most of the details of their exact implementation are kept secret to preserve the IP. However, most of the major components of the microarchitecture are well understood and I will provide a brief description in the following sections.

#### 2.1.1 Pipeline

Pipelined CPUs divide the life of an instruction within the microarchitecture into stages. While an instruction moves from one stage to the next, it opens up the possibility for a new instruction to start using the stage left empty. This allows the CPU to maximize the use of each stage of the pipeline without waiting for a single instruction to cross all the stages. This type of microarchitectural design allows to achieve instruction-level parallelism in a single processor. The number of stages inside the pipeline hugely depends on the CPU designs. It can variate from 2 to more than 30 stages.

#### 2.1.2 Cache

Another optimization that can be found in modern microarchitecture design is the cache. The cache is a very fast piece of memory that is placed closer to the execution units so that most-used data does not need to be retrieved always from main memory. In today's CPUs there are several

layers of caches some of which are shared across all cores on the system and others that are instead private of a specific core. Each cache hierarchy implementation differ in the number of levels, dimensions, addressing technique and policies under which they operate. In the context of cache side channels attacks, it is critical to understand how the cache hierarchy works under the microarchitecture that is target of the attack.

#### 2.1.3 Branch Prediction

Among the most common instructions that can be found in most programs there are branch or jump instructions, which role is to transfer the control flow to an arbitrary location instead of the next instruction in the flow. To optimize the pipeline, the CPU needs to know ahead of time which will be the next instruction to fetch. While this is a relatively easy task when dealing with direct jump/branch instructions, it is a very complex operation when the CPU needs to predict indirect branches in which the target is computed at runtime and it might change at each execution. To solve this issue, modern microarchitectures employ branch predictor units that are complex machinery which, by looking at the history of a specific branch, try to predict the next possible target for a specific indirect branch. An example of a modern branch predictor unit is TAGE [8] that is believed to be the based of many today's predictors.

### 2.1.4 Out-of-order Execution

The idea behind out-of-order execution is to allow stream of instructions, that are data independent, to be executed outside the original order in which the program was written. This optimization kicks in whenever an instruction causes a stall while waiting for data from main memory. In many situations, it is possible that downstream some instructions are already ready to go into execution because they do not depend on the stalled instruction. The CPU starts executing those instructions in parallel to keep the pipeline utilized. However, after execution these most recent instructions will be waiting for the stalled instruction to retire to officially be committed at the architectural level. This of course is done by the CPU to maintain the semantic of the program.

#### 2.1.5 Speculative Execution

Speculative execution is one of the most critical optimizations of modern CPUs. There are several situations in which the microarchitecture might require to stall due to events such as a slow branch resolution. While with out-of-order execution the pipeline is filled with an independent stream of instructions that are found downstream, during speculative execution the CPU tries to guess which is the outcome of the stalled instruction and based on that guess it will start to execute dependent instructions to the one that has stalled. By doing so, the instruction stream can continue in the hope that the guess done by the CPU by using one of the many predictors available is correct. If the guess was not correct, the instructions executed are squashed and the CPU will restart the execution with the correct result. In the case in which the guess is correct thought, the CPU has saved several CPU cycles by not waiting the resolution of the stalled instruction.

#### 2.1.6 Multiprocessing and multithreading

In the early stages of computing, most of the performance was obtained by raising the clock frequency of the CPU. However, due to physical limitations such as heat dissipation, since the late 90s two new techniques are introduced to obtain instruction level parallelism: multiprocessing and multithreading. In the first, the microarchitecture is equipped with multiple cores that are able to run more processes at the same time. In the second, each core is able to run different threads of the same program in parallel which allows to explicitly exploit the parallelism of several operations that would be otherwise sequentially executed within the context of a single program. A key difference between multiprocessing and multithreading is that in the case of multithreading the two threads might share several internal structures of the same core while that is not the case for two processes running on different cores.

## 2.2 Transient execution attacks

Transient execution attacks exploit a new class of vulnerabilities, targeting a particular microarchitectural CPU design with specially crafted software. These attacks leverage known attack vectors such as side channels, but go much further by combining them with vulnerabilities at the microarchitectural level. Numerous variants of transient execution attacks have been disclosed since the beginning of 2018.

Transient execution attacks are commonly divided into two major families: *Speculation-based* and *Fault-based* [9]. The *Speculation-based* family includes the various Spectre variants that leverage speculative execution to achieve data exfiltration. I refer to this family of attacks as *Speculative Execution Attacks*. The *Fault-based* family instead, comprises of all the Meltdown variants that rely on bugs in the way the CPU handles faults and out-of-order execution to achieve similar results.

#### 2.2.1 Fault-based attacks

The Meltdown family of attacks exploits bugs within the CPU. During a Meltdown attack, the attacker tries to perform operations speculatively that are not allowed due to privilege boundaries. Meltdown relies on the fact that faults are handled by the CPU only when the faulty instruction retires, leaving the out-of-order execution to continue across privilege boundaries before the fault is registered. This can allow an attacker to create a cache side channel with data retrieved from a higher privilege level through out-of-order execution. Each variant of Meltdown exploits a different fault type.

While these attacks are powerful and relatively easy to perform, they are easily fixable and meant to disappear in future iterations of the CPU, i.e., they are less interesting from the research point of view.

#### 2.2.2 Speculation-based attacks

In modern CPUs, speculative execution is employed in several situations to boost performance and avoid bottlenecks in the execution pipeline. For instance, whenever a conditional branch is encountered in the instruction stream and one of the operands is not readily available, the CPU speculates the result of the conditional branch and continue to execute further instructions. When the uncached operand is finally loaded from the main memory and the conditional branch can resolve, the CPU verifies the correctness of the guess and either commit and retires the speculated instructions, if the guess was correct, or rollback otherwise. Similarly, speculative execution is also triggered when the destination of an indirect call is not cached.

Spectre [4, 10] was the first to shows that whenever a mis-speculation take place, the CPU might execute code that access sensitive data leaving side-effects in the micro-architecture. Such side-effects, that before were considered not accessible from outside the micro-architecture, can actually be observed through a side-channel. A critical factor for the feasibility of these attacks is that the attacker can force such mis-speculation through training of the particular predictor unit that is involved in the attack.

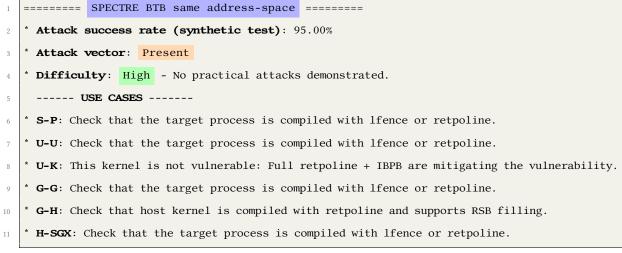

Speculative execution attacks can be further classified according to where the training of a predictor occurs. In particular, I define the following relevant configurations: *i*) *same address-space* (sAS) where training occurs in the same address space as that of the victim process, or *ii*) *cross address-space with simultaneous multi-threading* (cHT) where training occurs in a separate process running on the same physical core, or *iii*) *cross address-space without simultaneous multi-threading* (cAS) where training occurs between two processes running interleaved on the same physical core. Note that the cHT setting is a setting where attacker training and victim speculation occur in temporal colocation (different logical core, same time), whereas in the cAS setting they occur in spatial colocation (same logical core, different time). These settings are important because several attacks and mitigations rely on them. Thus, considerations on the specific setting must be taken into account in the threat model when evaluating the security posture of a system.

#### 2.2.3 Speculative Execution Attacks Phases

Speculative execution attacks can be decomposed into the following five distinct phases:

- Prepare side channel: In this phase, the CPU performs operations that will increase the chances of the attack succeeding. For instance, the attacker can prime caches to prepare for a prime-and-probe [11] cache side channel measurement, make sure important target data is flushed, or ensure that the attacking thread and victim thread are co-located.

- II) Prepare speculative execution: In this phase, the CPU executes code that will allow speculative execution to start. This is code that is typically executed within the context of the victim.

- III) Speculative execution start: In this phase, the CPU executes an instruction whose outcome decides the next instruction to be executed, such as a conditional branch instruction. Between the time window where this instruction is issued and when it is retired, modern CPUs guess the outcome of the branch to avoid stalling the pipeline, and execute code speculatively. This is known as speculative execution [12].

- IV) **Speculative execution, side channel send**: In this phase, the CPU executes (but does not retire) instructions that will result in a micro-architectural state change.

V) **Side channel receive**: In this phase, the CPU executes instructions that transform the micro-architectural state change that occurred in the previous step into an architectural state change.

### 2.3 Privilege boundaries and attack impact

The core element that turns transient execution into an attack is the breach of a privilege boundary that is established through hardware isolation support by the CPU. These privilege boundaries typically aim to provide confidentiality and integrity of the data residing within the boundary (i.e., preventing data from being read or modified directly from outside the boundary). All accesses to such data are mediated by code running within the privilege boundary, and that code may only be invoked from a lower privilege through well-defined entry points.

In the case of currently known speculative execution attacks, the attacker's aim is limited to breach confidentiality of data residing beyond the privilege boundary by either accessing arbitrary data or leaking specific metadata, such as pointer values, of the running program. For instance, privilege boundaries that can be bypassed by some known speculative execution attacks are:

- kernel vs. user-mode code

- hardware enclave (SGX) vs. user-mode or kernel-mode code

- sandboxed code in the same process, for example JavaScript JIT code

- processes-to-process boundary

- remote node to local node boundary

I note that code at each speculative execution attack phase previously described (Section 2.2.3) can potentially be run either in the higher privileged mode (victim-provided code) or lower privileged one (attacker-provided code).

## 2.4 Defenses

Several mitigations have been developed to protect against transiet execution attacks. Some of these mitigations repurpose existing instructions or sequence of instructions to block speculative execution in sensitive areas of the code. To this category belong memory fencing instructions (e.g., *lfence*), brancheless masking [13], and Retpoline [14]. Others, instead, are new hardware features that hardware vendors introduced in new iterations of the CPU. Changes are also made at the operating system level, including the re-design of entire subsystems.

#### 2.4.1 Memory Fencing

Through the application of serialization instructions, such as *lfence* on Intel, it is possible to force the CPU pipeline to wait for prior instructions to retire and, as a consequence, to block speculation and related Spectre attacks. Such a pipeline interruption is an expensive operation, therefore fencing instruction should be placed carefully either manually or at compile time only where really needed. For instance, the Linux kernel uses manually instrumented code, if the Spectre mitigations are enabled.

### 2.4.2 Branchless masking

Branchless masking is a mitigation against Spectre-PHT attacks to harden load instructions that are gated by a condition. The technique involves introducing a *data* dependency (usually called mask) on the condition through a set of instructions which set the mask to zero in case the condition is false (and to unsigned negative one otherwise). The mask is then used to zero out pointers or array indices before performing the load when invalid. Masking is for example used in the Linux kernel [15] to block Spectre-PHT whenever a value coming from userspace is used as an index for an array access. It is also available as a compiler option (Speculative Load Hardening (SLH) [16]) to instrument conditional branches with control-flow dependent pointer masking.

## 2.4.3 Retpoline

As an answer to Spectre-BTB, the Retpoline [17] compile-time mitigation replaces indirect branches with *ret* instructions to prevent branch poisoning. This method ensures that return instructions always speculate into an endless loop through the RSB.

## 2.4.4 KPTI

KPTI mitigates Meltdown-US and fortifies KASLR. KPTI is based on KAISER [9] (short for *Kernel Address Isolation to have Side-channels Efficiently Removed*). If KPTI is enabled, whenever userspace code is running, Linux ensures that only the kernel memory pages required to enter and exit syscalls, interrupts and exceptions are mapped. With no other pages mapped, KPTI prevents the use of kernel virtual addresses from user-space because they cannot be correctly translated.

## 2.4.5 Indirect Branch Restricted Speculation

Indirect Branch Restricted Speculation (IBRS) [18] prevents indirect branch predictors executed in privileged code from being trained by less privileged code (i.e kernel-space cannot be influenced by user-space). This also includes the case of attacks from another logical core on the same physical core (cHT).

### 2.4.6 Indirect Branch Predictor Barrier

Indirect Branch Predictor Barrier (IBPB) [19] prevents code that executes before it from affecting branch prediction for code that executes after. When enabled, an IBPB barrier runs across user mode or guest mode context switches. In this way, a different user cannot attack a process of another user running on the same machine. On Linux machines, IBPB can be conditionally or fully enabled: in the first case, the barrier is raised only when switching to processes that request it using *seccomp* or *prctl*.

## 2.4.7 Single thread indirect Branch Predictors

Single Thread Indirect Branch Predictors (STIBP) [20] splits the branch predictor across sibling threads of a core, removing the attack vector constituted by a process training the predictor of a co-located victim process. This prevents attacks like Spectre-BTB in the cHT setting.

### 2.4.8 RSB filling

RSB filling blocks Spectre-BTB and Spectre-RSB in the cAS setting. It flushes the RSB whenever the CPU switches across privilege levels. For instance when the CPU switches from usermode to kernel mode the RSB might contain poisoned entries introduced by the attacker which might affect its speculative control flow. The process of RSB filling removes any such entry.

### 2.4.9 SSB mitigation

When software-based mitigations are not feasible (such as inserting an *lfence* instruction between the store and the load instructions) for Spectre-STL, some CPUs support Speculate Store Bypass Disable that can be used to mitigate speculative store bypass. When SSBD is set, loads will not execute speculatively until the address of older stores are known.

### 2.4.10 PTE inversion

PTE inversion is used to block Meltdown-P attacks. When a page table entry points to a non present page, the upper address bits are inverted so that an access to such entry resolves to uncacheable memory access. Given that Meltdown-P can only exfiltrate data from L1 cache, forcing the address translation to return an uncacheable address closes the attack vector.

## 2.4.11 VMC conditional

VMC conditional cache flushing is adopted on virtualized environments. The mitigation flushes the L1 cache at every VMENTER instruction. This way secrets possibly stored in the cache are no longer accessible via the Foreshadow-VMM attack.

## Chapter 3

## **Related Work**

### 3.1 Speculative Execution

Optimizing CPU instruction throughput through speculative execution has been extensively analyzed and implemented in the 1990s [21, 12, 22]. For information about the microarchitecture of CPUs with respect to out-of-order and speculative execution, I mostly have to rely on the material provided by the CPU manufacturers [23, 24, 25]. Unfortunately this material often just provides software performance optimization related aspects, not providing details on how mechanisms such as the branch predictor work. Agner Fog's work [26] sheds light on those details, providing detailed information backed by a substantial amount of experimental research on the microarchitectural aspects of CPUs. This information is leveraged in processor simulators such as gem5 [27].

## 3.2 Cache Side Channels

Many speculative execution attacks variants rely on cache side channels to infer the memory contents accessed by speculative execution. Cache side channels have been extensively studied: First, Tromer et al. introduced both the "evict-and-time" and "prime-and-probe" techniques to efficiently perform a cache attack on AES [11]. Prime and probe is a popular technique, which was also used for certain speculative execution attacks variants. "Flush-and-reload" [28] is a technique that allows for higher precision and is used in NetSpectre. Recently, other techniques such as "flush-and-flush" [29] and "prime-and-abort" [30] were presented. Flush and flush leverages the fact that *clflush* executes faster in case of a cache hit. Prime and abort makes use of Intel's transactional memory mechanism to detect when an eviction has happened without the need to probe the cache.

## 3.3 Speculative Execution Attacks

Speculative execution attacks comprise those leveraging microarchitectural components such as the Pattern History Table (PHT) for Spectre v1 [10], the Branch Target Buffer for Spectre v2, the Return Stack Buffer (RSB) for Ret2Spec [31] and Spectre returns [32]. Both BTB and RSB attacks

are cases of speculative control flow hijacks, i.e., they provide the ability for an attacker to steer speculative execution to an arbitrary location. Varied and powerful attacks leveraging the BTB for speculative control flow hijacks have been demonstrated, in combination with port contentionbased, instruction cache-based, or BTB-based side channels [33, 34]. In Spectre v1.1 [35], Kiriansky and Waldspurger point out that speculative overwrites of backward edges lead to speculative control flow hijacks.

In practice, BTB gadgets are hard to find, thus attacks have only been shown to be practical if the gadget is injected (e.g., by loading attacker-controlled eBPF bytecode into the kernel). The idea of chaining speculative gadgets in a way similar to ROP was suggested shortly after the first publication of Spectre attacks. Some publications have referred to the same idea [35, 33], the former only briefly mentioning speculative ROP attacks but practical aspects are neither discussed nor experimented on.

Netspectre [36] introduces a victim data eviction technique based on coarse-grained cache eviction. The method, *Thrash+Reload*, is a remote variant of *Evict+Reload* [37]. The attacker starts a large file download from the victim via a network interface. On the victim's side, this action results in victim data eviction with a probability which depends on the file size. *Thrash+Reload* applicability is limited to scenarios where cache thrashing does not compromise the attack.

### 3.4 Mitigations

Since the first speculative execution attacks have been disclosed in early 2018, different mitigations have been proposed to prevent each variant. Some mitigations are introduced at hardware level meanwhile others are software-based. Many of these mitigations target Spectre v2 type of attacks, meanwhile no software-transparent mitigation has been introduced for Spectre v1.

The available software-based Spectre v1 mitigations consist in either deploying a serializing instruction (e.g., *lfence*) around each sensitive bounds check or, alternatively, masking the index used for accessing arrays [13, 38, 35, 39].

While *lfence* is an effective mitigation, it incurs huge performance penalties if widely applied. Static analysis tools have been proposed to search for sensitive code patterns. One example is the Linux kernel where vulnerable code is instrumented on a case by case basis either through manual audit or automatic tools (e.g., smatch [40]) detection [41]. The drawback of current available tools is that they target Spectre v1 code patterns such as array-out-of-bounds cases only and therefore are not useful in the general memory corruption case (where an overwrite of a control-flow influencing value can occur for any other mispeculation). Due to the high overhead, big projects like JavaScript engines deployed alternative techniques against Spectre v1 such as diluting timing precision, disabling concurrent threads to prevent homebrew-timers and masking pointer accesses to prevent speculative out-of-bounds accesses [42, 43, 44].

For Spectre v2 instead, there are software and hardware mitigations. The software mitigation currently available is Retpoline [14]. This mitigation targets indirect calls and indirect jumps and prevents them from being speculatively executed by trapping speculation within a loop. As in the barrier cases for Spectre v1, Retpoline requires code modification and therefore each program has to be recompiled to enforce such mechanism. Linux has deployed Retpoline in the kernel as mitigation for Spectre v2.

On the hardware side, Intel published three major protections: *i*) Indirect Branch Restricted

Speculation (IBRS) [18], which prevents speculation of indirect branches using target values computed using lower privileged predictor modes, *ii*) Single Thread Indirect Branch Predictors (STIBP) [20], which prevents *Branch Target Buffer* (BTB) poisoning from sibling threads, and *iii*) Indirect Branch Predictor Barrier (IBPB) [19], which ensures that code before a barrier does not influence the behavior of the code after. IBRS and IBPB are meant to protect higher privileged code from lower privileged code. The only mitigation that provides protection within the same privilege level is STIBP, which is not enabled by default for performance reasons.